U31X4-PCIE8XE101

Quad Channel 8-port (2-port x 4) USB 3.1 Gen 2 to PCI Express x8 Gen 3 Host Card

Highlights

- Host Bus: PCIe x8 Gen 3 (8.0 GT/s)

- Compliant with PCI Express Base Specification Revision 3.0

- Four independent USB 3.1 Gen 2 (10Gbps) Host Controllers

- Compliant with Universal Serial Bus 3.1 specification Revision 1.0

- Compliant with Intel’s eXtensible Host Controller Interface (xHCI) specification Revision 1.1

- Eight USB 3.1 Cable Ports (A-type Receptacle)

- Provides USB 3.1 cable port lock mechanism

- 5.25" ODD Form Factor (DU31X2-IPCIE2XG322)

Introduction

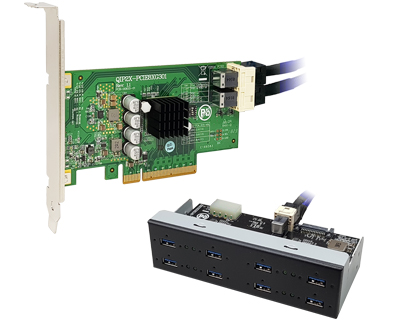

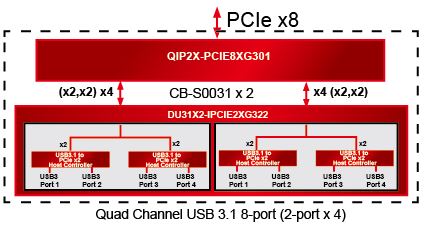

The U31X4-PCIE8XE101 is an Quad channel 8-port (2-port x4) USB 3.1 to PCI Express x8 Gen 3 Host Card.

U31X4-PCIE8XE101 is integrated by the following three key parts (QIP2X-PCIE8XG301, DU31X2-IPCIE2XG322, CB-S0031).

- QIP2X-PCIE8XG301

- Internal Dual PCIe x4 (two SFF-8643 Connectors) to PCIe x8 Gen 3 Switch Host Card

- DU31X2-IPCIE2XG322

- Integrated four USB 3.1 Gen 2 (10Gbps) to PCIe x2 Gen 3 (8Gbps) Host Controllers (Asmedia ASM3142, USB IF TID 5080000010).

- Two CB-S0031

- SFF-8643 to SFF-8643 Cable, L=50cm

Utilizing the standard PCI Express Switch, the 16-Lane/5-Port PCI Express Switch provides the most efficient fan-out solution for integrating Quad PCI Express to USB 3.1 Single Chip Host controllers into a small board design. Each USB 3.1 to PCI Express Single Chip Host controller takes advantages of 10 Gbps burst rate of 8-lane PCI Express bus in both directions and is fully compliant with PCI Express Base specification r3.0. This solution provides full PCI Express and USB 3.1 functionality and performance.

Technical Specifications

QIP2X-PCIE8XG301

| Upstream PCIe interface |

|

||||||||||||||||||||||||

| Downstream PCIe interface |

|

||||||||||||||||||||||||

| Key Features |

|

||||||||||||||||||||||||

Lane Status LEDs

|

|

||||||||||||||||||||||||

| Switch | SW1-1&2: PCIe Port Configuration

SW1-3&4: Max PCIe Data Rate

|

||||||||||||||||||||||||

| Computer Platform Requirements | Desktop computer equipped with a PCIe 3.0 x8, x16 slot | ||||||||||||||||||||||||

DU31X2-IPCIE2XG322

| PCI Express |

|

| USB Features |

|

| Number of Ports | Eight USB 3.1 (Standard A-type Receptacle) cable ports |

USB3 cable lock mechanism |

|

| USB Bus Power Input | DC 12V (Step-Down) from either Big IDE 4-pin DC Power Connector or/and SATA 15pin Power Connector |